Product Summary

The HY5PS561621AFP-25 is a 256Mb DDR2 SDRAM.

Parametrics

HY5PS561621AFP-25 absolute maxing ratings: (1)VDD Voltage on VDD pin relative to Vss: - 1.0 V ~ 2.3 V; (2)VDDQ Voltage on VDDQ pin relative to Vss: - 0.5 V ~ 2.3 V; (3)VDDL Voltage on VDDL pin relative to Vss: - 0.5 V ~ 2.3 V; (4)VIN, VOUT Voltage on any pin relative to Vss: - 0.5 V ~ 2.3 V; (5)TSTG Storage Temperature: -55 to +100 ℃.

Features

HY5PS561621AFP-25 features: (1)VDD ,VDDQ =1.8 +/- 0.1V; (2)All inputs and outputs are compatible with SSTL_18 interface; (3)Fully differential clock inputs (CK, /CK) operation; (4)Double data rate interface; (5)Source synchronous-data transaction aligned to bidirectional data strobe (DQS, DQS); (6)Differential Data Strobe (DQS, DQS); (7)Data outputs on DQS, DQS edges when read (edged DQ); (8)Data inputs on DQS centers when write(centered DQ); (9)On chip DLL align DQ, DQS and DQS transition with CK transition; (10)DM mask write data-in at the both rising and falling edges of the data strobe.

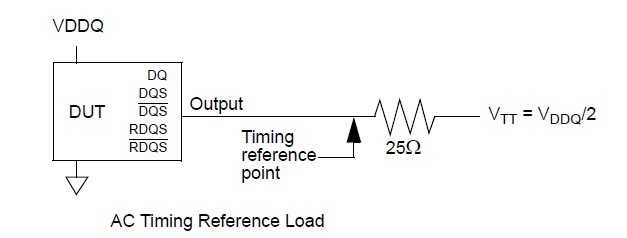

Diagrams

|

HY5PS121621F |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY5PS121621FP-C4 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY5PS121621FP-E3 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY5PS121621FP-Y5 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY5PS121621L |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY5PS121621LFP-C4 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Singapore)

(Singapore)