Product Summary

The MCF5280CVM66 is a processor core. It is comprised of two separate pipelines that are decoupled by an instruction buffer. The two-stage instruction fetch pipeline (IFP) is responsible for instruction-address generation and instruction fetch. The instruction buffer is a first-in-first-out (FIFO) buffer that holds prefetched instructions awaiting execution in the operand execution pipeline (OEP). The OEP includes two pipeline stages. The first stage decodes instructions and selects operands (DSOC); the second stage (AGEX) performs instruction execution and calculates operand effective addresses, if needed.

Parametrics

MCF5280CVM66 absolute maximum ratings: (1)Supply Voltage, VDD : – 0.3 to +4.0 V; (2)Clock Synthesizer Supply Voltage, VDDPLL: – 0.3 to +4.0 V; (3)RAM Memory Standby Supply Voltage, VSTBY: – 0.3 to + 4.0 V; (4)Flash Memory Supply Voltage, VDDF: – 0.3 to +4.0 V; (5)Flash Memory Program / Erase Supply Voltage, VPP: – 0.3 to + 6.0 V; (6)Analog Supply Voltage, VDDA: – 0.3 to +6.0 V; (7)Analog Reference Supply Voltage, VRH: – 0.3 to +6.0 V; (8)Analog ESD Protection Voltage, VDDH: – 0.3 to +6.0 V; (9)Digital Input Voltage, VIN: – 0.3 to + 6.0 V; (10)Analog Input Voltage, VAIN: – 0.3 to + 6.0 V; (11)EXTAL pin voltage, VEXTAL: 0 to 3.3 V; (12)XTAL pin voltage, VXTAL: 0 to 3.3 V; (13)Instantaneous Maximum Current, ID: 25 mA; (14)Maximum Power Supply Current, IDD: 300 mA; (15)Operating Temperature Range (Packaged), TA: – 40 to 85℃; (16)Storage Temperature Range, Tstg: – 65 to 150℃; (17)Maximum operating junction temperature, Tj: 105℃; (18)ESD Target for Human Body Model, HBM: 2000 V.

Features

MCF5280CVM66 features: (1)Static operation; (2)On-chip 32-bit address and data path; (3)Processor core and bus frequency up to 80 MHz; (4)Sixteen general-purpose 32-bit data and address registers; (5)ColdFire ISA_A with extensions to support the user stack pointer register, and four new instructions for improved bit processing; (6)Enhanced Multiply-Accumulate (EMAC) unit with four 48-bit accumulators to support 32-bit signal processing algorithms; (7)Illegal instruction decode that allows for 68K emulation support; (8)Real-time trace for determining dynamic execution path ; (9)Background debug mode (BDM) for in-circuit debugging; (10)Real time debug support, with one user-visible hardware breakpoint register (PC and address with optional data) that can be configured into a 1- or 2-level trigger.

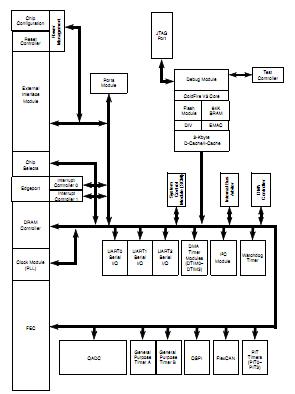

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

MCF5280CVM66 |

Freescale Semiconductor |

32-bit Microcontrollers (MCU) MCF5216 V2CORE NOFLASH |

Data Sheet |

|

|

||||||||

|

MCF5280CVM66J |

Freescale Semiconductor |

32-bit Microcontrollers (MCU) V2CORE NO FLASH |

Data Sheet |

|

|

||||||||

(Singapore)

(Singapore)